As Daniel has previously described here, this requires a system where every 512 1MHz CPU cycles:

1. The POT lines are connected to GND for 256 cycles.

2. The POT lines are disconnected from GND, and then the 256 cycles are counted until the POT line reaches a logical high level. This time is the reading on the pot.

The 1351 mouse detects this cycle, and then drives a pulse starting a certain time into the sequence based on the value it wants to communicate to the computer. Thus it is important that we replicate this scheme accurately.

As the current M65 r1 prototype PCBs lack POT lines on the joystick ports, we will temporarily use two of the IEC serial port lines for testing. This is because the IEC serial lines are controlled in a way that is the same as we need to be able to control the POT lines when we are pretending to be the SID chip, that is, we need to be able to pull a line to ground, and then to be able to release it to float, and that can be read in that state. It also happens that my IEC pull-up cable that I made to work around the lack of pull-ups on the r1 PCB gives me easy access to those lines already, and indeed, the lack of pull-ups means I can float those lines nice and easily.

So here is my plan:

1. Make a quick and dirty set of paddles, so that I have something to test with, before graduating to the 1351 mouse. This just consists of a pair of 500K Ohm variable resistors wired to the POTX and POTY lines on the joystick port, with the other side of the resistors tied to 5V. What I made to meet this need is in no way intended to be used to play games, and instead is totally minimal:

2. Wire up a shim cable for the joystick port, that routes the POTX and POTY lines to the IEC lines, and adds the 2.2nano Farad capacitors to ground. See the photos below of my construction of this cable:

First, connect GND, +5V and the digital lines straight through:

Second, add the capacitors (the small green jobs on the connector to the left), and then connect those lines to the exposed IEC data and clock signals on my existing IEC pull-up shim cable (you can also see the floppy power connector I added earlier in the day, as I started working on making the internal 3.5" floppy drive work -- more on that in another post):

Third, put cages on the ends of the cable:

Right, so now we have the Squid of Doom(tm), which if we plug the IEC cable in to the computer, and the joystick connector that is part of the pass through into the joystick port, we in theory have the electrical interface that will allow us to read the analog inputs.

3. Test!

The process for testing this, is to have the FPGA every 512 micro seconds pull the POT lines to ground for 256 cycles. To do this, we enable output on the IEC lines, to pull them to ground. Then, we disable the IEC outputs, and monitor the inputs for 255 micro seconds, and not at which point in time the signal is interpreted as a digital 1. That duration is the value returned.

While this is being cobbled together using existing signals, for the next revision of the main board, the whole arrangement will require only five lines to be able to monitor all four analog inputs simultaneously: 4x input lines for reading, and one output signal that causes all four lines to be pulled to ground. This will mean that it will be possible to have very simple code to read these lines on the MEGA65, as we will be able to hide the accuracy errors that arise from the analogue multiplexor on the C64, that multiplexes the four analogue inputs from the two joysticks to the two digitisers in the SID chip.

For initial testing, I will extend my test harness VHDL programme, so that it pulls the IEC lines down, and does the counting, and uses the value to draw bars of length proportional to the analogue signal. One of the reasons for trying this with my home-made "paddles", is that the 1351 mouse is a bit more sophisticated, and tries to sample the POT lines to work out when the SID is pulling them to ground. Thus I want to remove that complexity initially, incase the 1351 mouse doesn't recognise this initially. Also, with the variable resisters, it is easier to test the full range of values, and make sure that I have everything correct.

So, I plugged my Squid of Doom in, powered everything up, and I can see the bars, and if I turn the paddle all the way in one direction, then the bar is really short, and if I turn it the otherway, it is really long. So everything is there at a fundamental level. However, note that I said "is" really long, not "becomes" really long. I am seeing a rather digital response here, with the threshold somewhere below 250 Ohms, rather short of the 500K ohm full-swing of a paddle. Here is the two displays: It is either full, or empty, but not smoothly moving between (the purple/teal bar at the bottom is the one to watch):

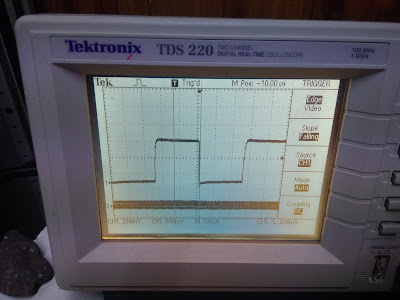

Hmmm.. Poking around to find the cause, I found one bug in my test harness: I was assuming a 50MHz input clock instead of 100MHz, so the scan rate was twice as fast as it should be, and thus the time for the pot lines to rise was only half what it should be. That said, on the oscilloscope I am seeing what otherwise looks like nice curves, although they are still rather too low at the high-resistance end of the pots:

Low resistance is fairly square:

Medium resistance is curvier:

And high resistance is almost flat:

This says to me that we probably need to have a shunt resistor added in there, so that the total resistance is lower. But first, we need to find out why we are reading only a rather digital signal. I have one of the inputs routed to an LED after it is digitised, and that LED varies in brightness quite smoothly, as you would expect from the variable duty-cycle digital reading of the signal.

So this means I have probably stuffed up my counter that works out what the pot value should be. This was indeed the case: I had the outpot enable line inverted, so that I was counting when the line was being pulled to ground, rather than in the gap. I can now pan smoothly across much of the range, although it is still not perfect. The two pot lines are partly coupled for a start. This could be that I have some touching wires somewhere, or some other minor horror to sort out. I'll take a look at that in the morning. However, I thought I would get my 1351 mouse out, just to see if this is working well enough to be able to convince the mouse to talk to us, and the answer is a definite yes, I can move the mouse around, and see the (still annoyingly coupled) pot lines respond.

My gut feeling for the coupling problem is that the two capacitors are touching, as they were quite close before I put the backshell on the DB9. Whatever the cause, once I have this sorted out, I will add the POT reading code to the MEGA65 VHDL, and make an option to route it to the IEC serial lines as I have done in the test harness, and then try reading it from the MEGA65 itself, perhaps using the 1351 test program or some other simple mouse-supporting program.

Nice to see how much progress you made in a day!

ReplyDeleteLikely some finetuning is necessary on the capacity of the capacitors and some additional resistance to get to the right values. I think the criterium for the size of the capacitor is the "sucking power" of the FPGA: It must be able to get the voltage below logic level within a single 1351 cycle. So there is an upper limit to the size of the capacitor.

A bit of additional resitance will be necessary to match the resistance of 500 kilo-ohms with the value 255. This depends on the logic level of the FPGA. It might be a good idea to put a second potmeter in between in order to determine the right value.

It is interresting that you are charging too slow: I don't see any good reason for this, without any additional resistance you would expect that you would charge too quickly. Don't forget to measure the exact voltage you are charging at, it does make a difference. The 1351 may not mind this too much, as it will charges the capacitor with 5V at high speed on the right cycle. But in order to read a correct paddle value, the resitance will need to be correct.

I think I know what the problem is, in fact. I could be wrong, but I can see exactly how things are being bridged, and how it would also be making it charge too slowly. There are probably just enough clues in the post above to work it out, if you can't wait in suspense for the next post on this topic ;)

DeletePaul.

Hmmmm.... you have connected your IEC-lines with 1000 Ohm resistors to 5V. But... doesn't that mean that there is an electrical connection between both pot lines (with 2000 Ohm in total in between)?

ReplyDeleteWell spotted, which would cause exactly the kinds of problems I was seeing. I have already bought a new DIN6 connector so that I can divide the Squid of Doom into two separate cables that do only one thing each, and do it properly. I'll be posting once I know whether it has worked.

Delete